Article Roundup: HLS for Automotive SoCs, SSD Verification with Emulation, IIoT in the UK, 7nm AMS Verification & the Channel Operating Margin

- High-Level Synthesis for Automotive SoCs

- Four Steps to Verifying An SSD Controller With Emulation

- IIoT Could Revolutionize UK Manufacturing, Says Siemens-led Report

- Silicon Creations Talks About 7nm IP Verification for AMS Circuits

- How Channel Operating Margin helps Gigabit Ethernet PCB analysis

High-Level Synthesis for Automotive SoCs

SemiWiki

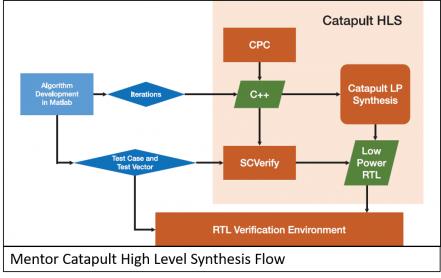

ADAS and autonomous applications require complex SoCs with an array of processors and accelerators for real-time image processing. Bosh found that incorporating high-level synthesis into their SoC design flow enabled them to optimize complex designs, despite evolving specifications.

ADAS and autonomous applications require complex SoCs with an array of processors and accelerators for real-time image processing. Bosh found that incorporating high-level synthesis into their SoC design flow enabled them to optimize complex designs, despite evolving specifications.

Four Steps to Verifying An SSD Controller With Emulation

Semiconductor Engineering

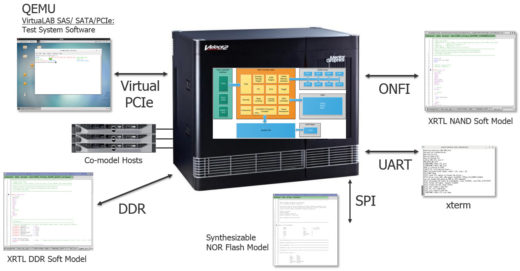

The complex controllers of solid state drives must perform a myriad of tasks to receive, monitor and deliver data accurately and reliably. Emulation is an ideal choice to verify these controllers because it is faster than simulation, runs real production firmware, and does pre- and post-production silicon verification from the same setup. This article details four steps to verifying SSD controllers with emulation.

The complex controllers of solid state drives must perform a myriad of tasks to receive, monitor and deliver data accurately and reliably. Emulation is an ideal choice to verify these controllers because it is faster than simulation, runs real production firmware, and does pre- and post-production silicon verification from the same setup. This article details four steps to verifying SSD controllers with emulation.

IIoT Could Revolutionize UK Manufacturing, Says Siemens-led Report

Internet of Business

A recent independent report, chaired by Siemens CEO Juergen Maier, concluded that the UK could achieve economic gains of £455 billion over the next 10 years by investing in the digitalization of manufacturing. Read more about the economic and societal impact of the IIoT in this article.

Silicon Creations Talks About 7nm IP Verification for AMS Circuits

SemiWiki

IC design at 7nm requires additional analysis to fix problems like increased impact from parasitic RCL values and slower circuit propagation due to interconnect resistances. Silicon Creations achieved first-pass success on their first 7nm silicon for AMS IP by using state-of-the-art EDA tools to conduct analysis early in their design process.

IC design at 7nm requires additional analysis to fix problems like increased impact from parasitic RCL values and slower circuit propagation due to interconnect resistances. Silicon Creations achieved first-pass success on their first 7nm silicon for AMS IP by using state-of-the-art EDA tools to conduct analysis early in their design process.

How Channel Operating Margin helps Gigabit Ethernet PCB analysis

Tech Design Forum

For high-speed PCB designs that support Gigabit Ethernet, the channel operating margin (COM) is an emerging algorithm-based methodology for ensuring compliance of the transmitter, receiver, and channel. Using COM reduces over-design while still attaining compliance for high-speed signals up to 28 gigabits. Learn more about how to implement COM in this article.

Comments

Leave a Reply

You must be logged in to post a comment.

جميل