Tech Updates: PCB Design Reliability, Portable Stimulus, Autonomous Vehicles, MPSoC Safety & Security, HDAP Trends

- Using Vibration and Acceleration Analysis to Improve Reliability

- Automating Test from IP to SoC Levels with Portable Stimulus

- Centralized Processing for Autonomous Vehicles

- Achieving Separation on Multiprocessor SoCs for Enhanced Safety and Security

- High Density Advanced Packaging Trends

Using Vibration and Acceleration Analysis to Improve Reliability

iConnect 007

For PCB designs, deriving the physical constraints and fatigue issues prior to manufacturing is essential to reducing board failure. By adding virtual vibration and acceleration simulation during layout, design teams have the ability to identify critical issues before the product goes into production.

For PCB designs, deriving the physical constraints and fatigue issues prior to manufacturing is essential to reducing board failure. By adding virtual vibration and acceleration simulation during layout, design teams have the ability to identify critical issues before the product goes into production.

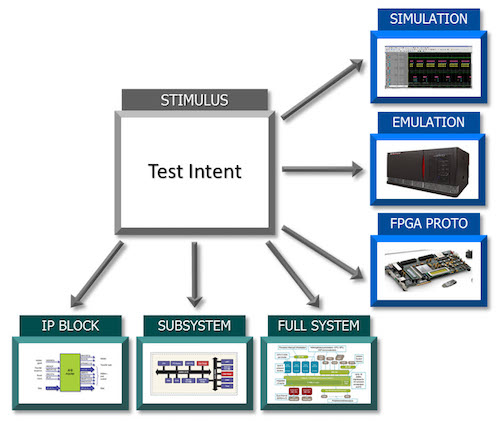

Automating Test from IP to SoC Levels with Portable Stimulus

Tech Design Forum

Improving design verification productivity and quality-of-results for complex SoCs requires a new approach. Find out about all the details on how the Accellera Portable Stimulus Specification (PSS) enables a single description of test intent that can be used across a variety of verification platforms—from IP-level to SoC-level verification.

Improving design verification productivity and quality-of-results for complex SoCs requires a new approach. Find out about all the details on how the Accellera Portable Stimulus Specification (PSS) enables a single description of test intent that can be used across a variety of verification platforms—from IP-level to SoC-level verification.

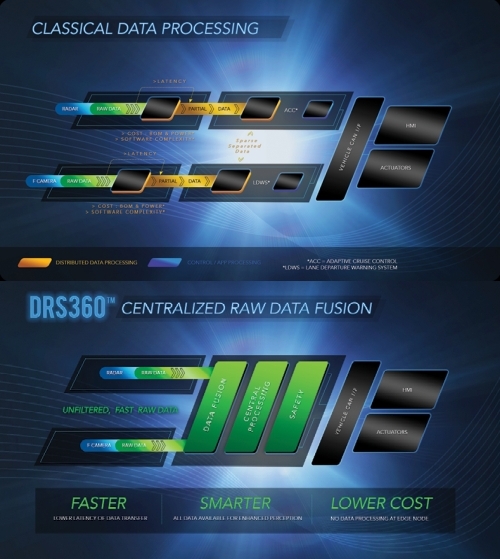

Centralized Processing for Autonomous Vehicles

Microcontroller Tips

ADAS data challenges remain for reaching full Level-Five autonomy (the vehicle can safely drive itself with no human input in any/all conditions). But centralized, raw-data platforms, like DRS360, provide an efficient way to identify events and regions of interest around a vehicle, and then combine the raw data from multiple sensor modalities to classify objects and ultimately make real-time decisions, enabling automated driving.

ADAS data challenges remain for reaching full Level-Five autonomy (the vehicle can safely drive itself with no human input in any/all conditions). But centralized, raw-data platforms, like DRS360, provide an efficient way to identify events and regions of interest around a vehicle, and then combine the raw data from multiple sensor modalities to classify objects and ultimately make real-time decisions, enabling automated driving.

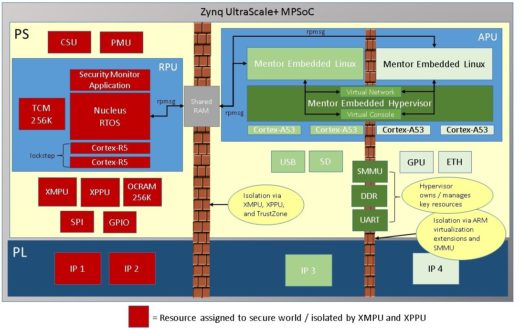

Achieving Separation on Multiprocessor SoCs for Enhanced Safety and Security

Semiconductor Engineering

Isolation is the overarching problem when it comes to both safety-critical software and software performing security functions. The Xilinx UltraScale+ MPSoC is used for both safety and security purposes, and the requirements for both areas are definitely starting to blur. This article demonstrates the different hardware mechanisms used for subsystem isolation.

Isolation is the overarching problem when it comes to both safety-critical software and software performing security functions. The Xilinx UltraScale+ MPSoC is used for both safety and security purposes, and the requirements for both areas are definitely starting to blur. This article demonstrates the different hardware mechanisms used for subsystem isolation.

High Density Advanced Packaging Trends

SemiWiki

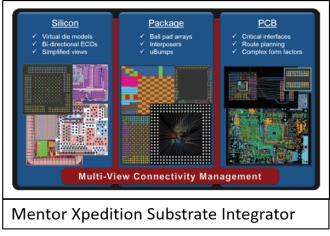

Get the details on a recent DAC half-day seminar on ‘High Density Advanced Packaging Trends’ with a focus on FO-WLP (Fan-Out Wafer-Level Packaging). Two industry guest speakers shared their experience with the technology and Mentor showcased their latest technologies and solutions followed by live technology demonstrations.

Get the details on a recent DAC half-day seminar on ‘High Density Advanced Packaging Trends’ with a focus on FO-WLP (Fan-Out Wafer-Level Packaging). Two industry guest speakers shared their experience with the technology and Mentor showcased their latest technologies and solutions followed by live technology demonstrations.

Comments

Leave a Reply

You must be logged in to post a comment.

Thank you, Mentor, for sharing the latest updates or all about PCB’s. I am really glad to read your blogs daily.