Article Roundup: Wally Rhines’ DVCon Keynote, IoT Edge, PCB Design, Co-Emulation, and Nucleus RTOS

- Wally Rhines Looks beyond ‘Endless Verification’ To the System Era

- IoT Edge Design Demands a New Approach

- The 4C’s of PCB Design

- Hardware-Assisted Verification, From Its Dawn to SystemVerilog, UVM, and Transactors

- Nucleus SE – An Introduction

Wally Rhines Looks beyond ‘Endless Verification’ To the System Era

Tech Design Forum

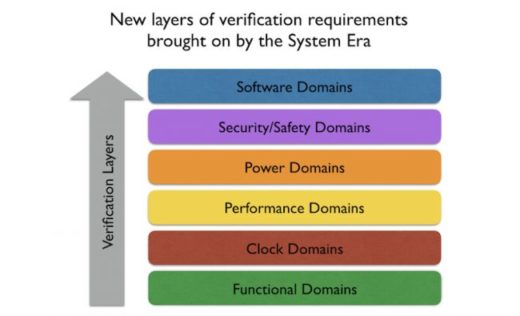

Wally Rhines offered a comprehensive overview of the challenges facing verification and how they are growing, during his keynote at the recent DVCon China. Emerging challenges, verification productivity, and targeted solutions were all covered. This article provides an overview of the keynote and four key takeaways.

Wally Rhines offered a comprehensive overview of the challenges facing verification and how they are growing, during his keynote at the recent DVCon China. Emerging challenges, verification productivity, and targeted solutions were all covered. This article provides an overview of the keynote and four key takeaways.

IoT Edge Design Demands a New Approach

Semiconductor Engineering

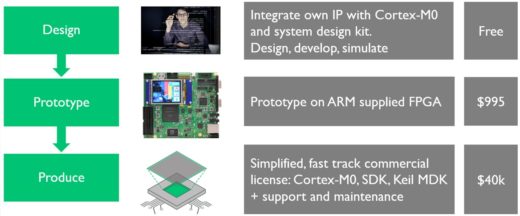

Today’s IoT edge device designers require low-cost proof-of-concept for their designs. ARM’s DesignStart portal allows designers fast and easy access to a trial selection of ARM products without charge. In addition, Mentor Graphics provides the Tanner EDA design tools for free evaluation and ARM offers approved design partners for SoC development help.

Today’s IoT edge device designers require low-cost proof-of-concept for their designs. ARM’s DesignStart portal allows designers fast and easy access to a trial selection of ARM products without charge. In addition, Mentor Graphics provides the Tanner EDA design tools for free evaluation and ARM offers approved design partners for SoC development help.

The 4C’s of PCB Design

SemiWiki

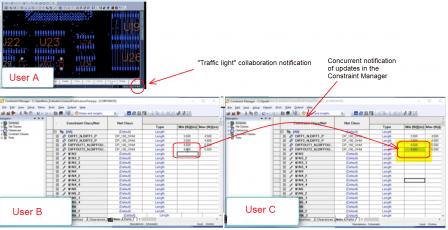

Mentor’s Xpedition PCB design platform addresses the 4C’s required by large, complex systems: Enabling a Collaborative, Concurrent environment, with data management features ensuring Consistency, across a site or Cloud-based project database.

Mentor’s Xpedition PCB design platform addresses the 4C’s required by large, complex systems: Enabling a Collaborative, Concurrent environment, with data management features ensuring Consistency, across a site or Cloud-based project database.

Hardware-Assisted Verification, From Its Dawn to SystemVerilog, UVM, and Transactors

EDN

Co-emulation gives verification teams a unique combination of performance, accessibility, flexibility, and scalability. This enables teams to move their verification strategy up a level of abstraction. Emulation experts provide a brief history of hardware-assisted verification – from the ICE age to today’s UVM transactors.

Co-emulation gives verification teams a unique combination of performance, accessibility, flexibility, and scalability. This enables teams to move their verification strategy up a level of abstraction. Emulation experts provide a brief history of hardware-assisted verification – from the ICE age to today’s UVM transactors.

Nucleus SE – An Introduction

Embedded.com

To better understand how an RTOS is implemented and deployed, Colin Walls walks readers through the design goals and objectives for creating the Nucleus RTOS. Top considerations include memory utilization, API implementation, scalability, and target users.

To better understand how an RTOS is implemented and deployed, Colin Walls walks readers through the design goals and objectives for creating the Nucleus RTOS. Top considerations include memory utilization, API implementation, scalability, and target users.