Article Roundup: Machine Learning, IP Qualification, Signal Integrity, Analog, and IPC APEX

- Functional Safety Standards in the Machine Learning Era

- IP Qualification during RTL Synthesis

- “Ten-hut!” Attending the Signal Integrity Bootcamp

- Devices Threatened By Analog Content?

- What the IPC APEX Event Didn’t Tell You

Functional Safety Standards in the Machine Learning Era

ISSUU

Autonomous vehicles controlled by machine learning technology starts with existing ISO 26262 standards. This in-depth article explores how we need to evolve verification safety requirements when considering complex learning systems such as neural networks.

Autonomous vehicles controlled by machine learning technology starts with existing ISO 26262 standards. This in-depth article explores how we need to evolve verification safety requirements when considering complex learning systems such as neural networks.

IP Qualification during RTL Synthesis

Semiconductor Engineering

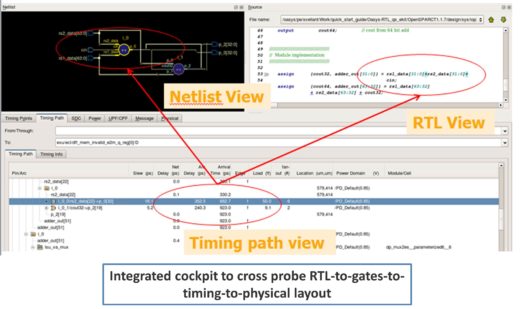

A next-generation RTL IP qualification and floorplanning flow lets RTL designers create and validate physically implementable RTL IP without having to depend on iterations with backend designers. The result is reduced iterations, reduced risk to schedule and improved IP quality.

A next-generation RTL IP qualification and floorplanning flow lets RTL designers create and validate physically implementable RTL IP without having to depend on iterations with backend designers. The result is reduced iterations, reduced risk to schedule and improved IP quality.

“Ten-hut!” Attending the Signal Integrity Bootcamp

SemiWiki

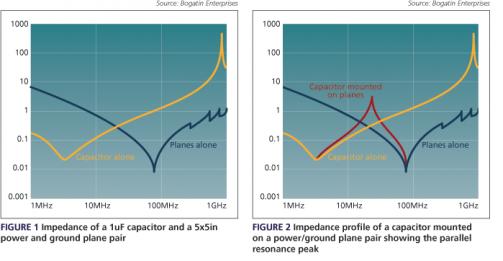

Signal integrity (SI) and power integrity (PI) engineers must be well-versed in a multitude of technical disciplines. Tom Dillinger attended a full-day intensive SI Bootcamp filled with a mix of lectures, labs, and questions from attendees. This article features Tom’s takeaways.

Signal integrity (SI) and power integrity (PI) engineers must be well-versed in a multitude of technical disciplines. Tom Dillinger attended a full-day intensive SI Bootcamp filled with a mix of lectures, labs, and questions from attendees. This article features Tom’s takeaways.

Devices Threatened By Analog Content?

Semiconductor Engineering

![]() Analog content in connected devices continues to grow at an astounding rate. With few measurable methods to assess analog quality, it’s not clear how that can impact safety-critical applications. Semiconductor Engineering tapped industry experts, including Mentor DFT gurus, to see how this issue is being addressed.

Analog content in connected devices continues to grow at an astounding rate. With few measurable methods to assess analog quality, it’s not clear how that can impact safety-critical applications. Semiconductor Engineering tapped industry experts, including Mentor DFT gurus, to see how this issue is being addressed.

What the IPC APEX Event Didn’t Tell You

EMS Now

IPC APEX 2017 emphasized the Open Manufacturing Language (OML) and the start of the IPC Connected Factory Initiative (CFI). Only these two standards can fulfill the needs of the PCB electronics assembly industry. Michael Ford offers his analysis.