A Powerful Analog Verification Platform for Samsung Foundry’s Advanced Technologies

Image: Courtesy Samsung Foundry

Having done IC development for over two decades, I can appreciate the complexities of foundry processes that influence device modeling and silicon fabrication. Semiconductor physics continues to get pushed to newer limits with each technology progression to a smaller process geometry to achieve better PPA (Power/Performance/Area). Chip developers are packing in more features to enhance the customer experience of the end product with focus on quality and reliability. Concurrently, EDA tools utilized for IC development continue to boost performance and capabilities to better equip the semiconductor eco-system to tackle the next big challenge. So where is the next technological innovation?

Samsung is a household name in consumer electronics for Mobile, Computing, TV & Audio, Appliances and Smart home products. Samsung Electronics’ semiconductor subsidiary takes it to the next level with industry leading solutions for memories, application processors, image sensors, displays, LED lighting and foundry technology. The foundry business that was initiated in 2005 was a tremendous leap that positively impacted the electronics world. Since then, Samsung Foundry has been innovating process technologies to serve the exponentially growing semiconductor chip business supporting global fabless and IDM semiconductor companies and has evolved into a premier manufacturer of low power, high performance SoCs.

An electronic circuit requires extensive and accurate simulations through various design stages leading to final tape out to realize accurate silicon correlation. It goes beyond just the circuit where design hierarchies, interconnects, loading and realistic stimuli need to be properly accounted for in its verification. Compromising on accuracy comes at a price of deviating away from product specifications and sometimes even catastrophic failures in hardware. In this era of complex data processing, the demand for smarter and more reliable electronic systems has exponentially increased across applications. These applications range across consumer, industrial, high performance computing, medical and automotive market segments. The hardware requirements for these intelligent systems have the primary need to pack more transistors in a small area while providing faster performance within power specifications. So how can the complexity of advanced semiconductor technologies be tackled effectively during design verification?

Denser and smaller ICs introduce added complexity for analog design and verification. Worsening device noise and increasing post-layout parasitics can significantly impact precision, hence requiring more complex design and verification techniques to compensate for process induced effects. This is especially the case for critical components dealing with high frequency data transport such as SerDes high speed links that are communication conduits within, between and outside chips. Such high-speed links that can support multiple data rates and protocol standards need careful and extensive verification with extracted simulations at many levels of design hierarchies. Similarly, data converters are critical IPs that convert digital to analog signals and vice-versa and are responsible for connecting the digital world to the analog world.

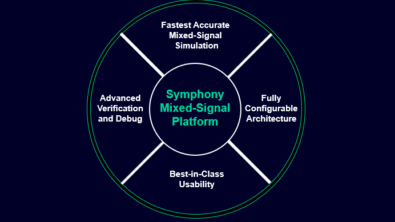

Verifying such precision systems requires a SPICE circuit simulator that can process the foundry’s complex device models while handling large netlists with the required foundry certified accuracy to get silicon correlation. Concurrently, fast simulations are required to achieve timely tape-outs. Here’s where we, Siemens EDA, come in with a comprehensive verification solution with our Analog FastSPICE Platform that caters to Samsung Foundry’s advanced technology nodes.

Samsung Foundry has a broad and scalable portfolio of FinFET and EUV technologies, and with ongoing investment and innovation in next-generation GAA technology. Their leading-edge processes at 7nm through 3nm GAA have variants for high performance computing and low power designs. Samsung’s Advanced Foundry Ecosystem, or SAFE™, is a program that enables deep collaboration between Samsung foundry, ecosystem partners, and customers to deliver competitive and robust System-on-Chip (SoC) designs. Siemens EDA is a proud EDA and Cloud partner in SAFE™ and provides supporting solutions for our mutual customers. Click here for further understanding of SAFE™.

Since 2019, Samsung Foundry has hosted an annual event called SAFE™ Forum which brings together their diverse customers and partners who are instrumental in nourishing the chip design industry. The Third SAFE™ Forum was virtually held from November 17th to December 17th, 2021. Here is the associated press release from Samsung on the event: Samsung and Its Foundry Partners Reveal Solutions for a Strong Design Infrastructure at 3rd SAFE Forum 2021

I had the pleasure of representing Siemens EDA’s AMS Business Unit in presenting a paper titled “Increase Analog IP verification throughput using Samsung Foundry’s 5LPE-3nm GAA with Siemens EDA’s Analog FastSPICE Platform”. In this presentation, I discussed the verification challenges seen by analog designers as they move to advanced process nodes and how the comprehensive features of Siemens EDA’s Analog FastSPICE™ Platform can tackle those challenges with nanometer-scale SPICE accuracy and superior simulation performance for post-layout verification. Furthermore, I summarized AFS simulation performance of circuits designed in Samsung’s advanced process nodes (5LPE, 4LPP and 3nm GAA) – specifically ADCs, Voltage regulators, SRAMs, Bandgaps, VCO and PLL that are crucial SoC building blocks. Siemens EDA’s partnership with Samsung Foundry for device and circuit level qualifications of its technology nodes is also showcased. Our collaboration with the Si2 CMC (Compact Model Coalition) for OMI (Open Model Interface) development to enable Samsung aging models in the CMC OMI interface is also discussed.

Click HERE to register to view the On Demand recording of AFS supporting Samsung advanced technology nodes.

To learn more about Siemens EDA’s AMS solutions and how we can address your IC development team’s most challenging analog/mixed-signal verification challenges, please visit our AMS product page.