How Symphony Pro is defining the future of mixed-signal verification for high-speed die-to-die interfaces: A case study by AnalogPort

A modern chiplet interface contains millions of transistors, thousands of control signals, and dozens of ultra-sensitive analog blocks, all of which must work together flawlessly at ultra-high frequency. How do you verify that?

This is a tough challenge many verification engineers are grappling with as the semiconductor industry accelerates toward chiplet-based architectures. The sheer scale and complexity of these mixed-signal interfaces have created a verification crisis that traditional methodologies simply cannot solve.

The problem runs deeper than complexity alone. High-speed die-to-die interconnects are intricate mixed-signal systems that demand two contradictory things simultaneously: transistor-level SPICE accuracy for analog signal integrity and digital-scale performance for comprehensive system verification. Traditional digital mixed-signal (DMS) flows use behavioral models that run fast but miss critical analog effects like crosstalk, jitter, and impedance mismatches. Meanwhile, analog mixed-signal (AMS) approaches deliver the precision you need but come with the cost of prohibitively large simulation times, manual signal connection overhead, and tool fragmentation that turns debug into a painstaking investigation.

For years, engineering teams have been forced into an impossible choice: sacrifice analog fidelity for speed or sacrifice productivity for precision. Neither option is acceptable when a single missed bug can cost millions of dollars in re-spins and many months of lost market opportunity.

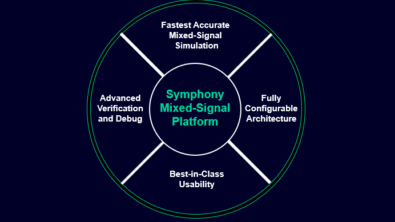

Symphony Pro: unified mixed-signal simulator that eliminates the compromise

AnalogPort, a leading provider of high-speed interface IP, overcame the verification bottleneck by utilizing Siemens EDA’s SymphonyTM Pro platform, part of SolidoTM Simulation Suite. Facing the challenge of verifying a complex 32 Gbps, 16-transmit/16-receive full-duplex die-to-die interface, AnalogPort needed a solution that could handle millions of devices while maintaining transistor-level accuracy where it mattered most.

The breakthrough? Symphony Pro’s ability to seamlessly integrate UVM-based digital verification with high-fidelity SPICE simulation without the manual overhead, tool fragmentation, or performance penalties that plague traditional approaches.

AnalogPort achieved these results through following essential capabilities of Symphony Pro:

- Automated Boundary Elements eliminated thousands of manual signal connections while enabling seamless transition between different net types, voltages, etc.

- Selective data dumping made large-scale verification practical by capturing only critical signals.

- Mixed-Signal Visualizer offered a seamless debug experience across the entire mixed-signal design hierarchy with comprehensive analysis, automation, and ease-of-use.

AnalogPort transformed its verification flow with Symphony Pro

AnalogPort successfully deployed their proven UVM methodology across the entire mixed-signal design, achieving comprehensive system-level verification while maintaining the analog accuracy critical for signal integrity validation. Symphony Pro’s accuracy, performance, and simulation mode options enabled verification strategies tailored to each block’s specific requirements, while the integration of QuestaTM platform’s digital simulator with Solido Simulation Suite’s SPICE simulator provided an industry-leading unified mixed-signal verification environment. This helped them meet aggressive project timelines that traditional approaches would have made impossible.

This isn’t just one company’s success story – it’s a blueprint for the entire industry. As chiplet architecture becomes standard, the verification challenges remain the same whether you’re designing Universal Chiplet Interconnect Express (UCIe), Bunch of Wires (BoW) interfaces, or custom die-to-die links: massive scale, mixed-signal complexity, and unforgiving performance requirements.

Ready to transform your mixed-signal verification flow? Download our whitepaper to discover the detailed methodology, technical insights, and practical strategies that made this breakthrough possible. Your next chiplet design deserves tools that don’t force you to choose between accuracy and productivity.