How Analogix utilized Solido SPICE to overcome verification challenges in creating high-quality PLLs

Analogix Semiconductor is a global provider of mixed-signal semiconductors, committed to advancing display quality on mobile devices while maximizing battery efficiency. Guided by their vision of “HD everywhere”, Analogix develops proprietary intellectual property using industry-standard interfaces to maintain circuit compatibility across targeted applications.

In September 2025, at the Solido Custom IC Forum in Beijing, Analogix demonstrated how they leveraged Solido SPICE to address challenges associated with phase-locked loop (PLL) design—a critical clocking component for high-performance display and connectivity solutions.

Challenges

PLL plays a key role in numerous systems, particularly in SerDes, where it supplies a stable clock for tasks like serialization, deserialization, jitter reduction, and frequency synthesis to accommodate various communication standards. As a result, having a high-quality PLL is essential for maintaining overall SerDes system stability. However, designing high-quality PLLs at Analogix faces three key challenges, primarily due to semiconductor advancements and strict noise performance requirements. Let’s discuss these challenges in detail:

Challenge 1: Device count

The required number of devices in a PLL rises swiftly as a result of fabrication limitations. These constraints drive the need to incorporate more devices into the design to achieve the desired performance and reliability levels. To ensure optimal matching and minimize noise, analog circuits must utilize complex compound devices. This complexity is essential for meeting the stringent requirements of advanced PLL designs, especially as noise performance becomes increasingly critical. Furthermore, device models are growing more intricate, often involving effects that extend beyond the capabilities of conventional Berkeley short-channel IGFET models (BSIM). As semiconductor technology progresses, capturing these advanced behaviors becomes necessary to accurately predict and optimize PLL performance.

Challenge 2: Simulation complexity

When evaluating simulation complexity for PLL designs, both the speed of the PLL and the number of devices involved play significant roles. Over the span of 17 years, from the advent of 45nm technology to current 2nm nodes, the complexity associated with simulating PLLs has experienced an enormous increase—approximately 1000 times greater. This dramatic escalation is a direct result of the need to accommodate higher device counts and faster PLL speeds, which drive up the intricacy of the simulation process. During the same period, advancements in CPU technology have not kept pace with the growth in simulation complexity. While top-of-the-line CPU performance has increased by about 35 times, this improvement is modest in comparison to the 1000-fold rise in PLL simulation complexity. Consequently, the gap between the computational requirements for accurate PLL simulations and available hardware performance has widened substantially, presenting significant challenges for designers seeking both precision and efficiency in their work.

Challenge 3: High accuracy and performance required

Designing phase-locked loops (PLLs) at Analogix presents significant challenges regarding simulation accuracy and performance. Achieving PLL lock requires lengthy simulation times, especially when working at the full SPICE level with extracted netlists. High accuracy settings must be maintained to properly evaluate jitter and phase noise, necessitating the reduction of simulator-generated noise. Transient noise analysis is essential for accurately characterizing device noise, which becomes increasingly important as the noise frequency at the output rises. This increase in noise frequency restricts each simulation time step, further complicating the process.

Additionally, measuring phase noise at low offset frequencies demands extended transient simulation times. The complexity intensifies during post-layout simulations, which are even more demanding. Such simulations require advanced matrix solvers and effective RC reduction algorithms to ensure reliable results and manageable computational loads.

Custom IC Solutions by Siemens EDA

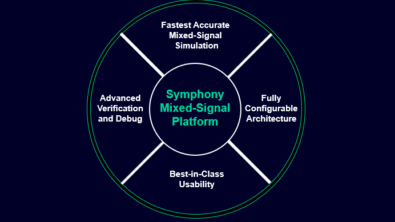

Solido SPICE, part of the Solido Simulation Suite, was launched in June 2024. Incorporating all Analog FastSPICE (AFS) capabilities, Solido SPICE offers comprehensive RF and transient noise analysis features designed to address the complexities of systems integrating phase detectors, charge pumps, VCOs, and dividers, as commonly found in PLL architectures.

Fig.1 Summary of Solido SPICE features

Additionally, leveraging the advanced solver and RC reduction technology, Solido SPICE is capable of managing larger designs and demonstrates superior performance—achieving up to a 45x speedup —while maintaining high accuracy.

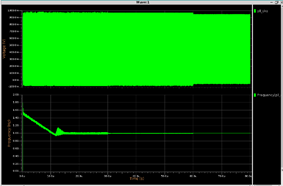

Fig.2 Solido SPICE’s comprehensive RF and transient noise offering

Analogix selected Solido SPICE to address the complexities associated with PLL design. In post-layout simulations involving 4,000 transistors, Solido SPICE efficiently produced results in 9 hours, compared to the 28 hours achieved from an alternate solution, for an overall speedup of 3.1x. Furthermore, Solido Waveform Analyzer streamlined comprehensive post-processing of simulation data, offering a range of built-in features that significantly aid in evaluating the PLL’s figure of merit.

Fig.3 Solido SPICE delivered accurate transient noise results, clearly displayed in Solido Waveform Analyzer

Fig.4 Solido Waveform Analyzer provides comprehensive built-in capabilities for thorough PLL verification

Acknowledgements

Thank you Analogix for adopting Solido Custom IC solutions for PLL development.