**Digital Industries Software**

## Why is a comprehensive workflow essential for chiplet design and today's 3D IC architectures?

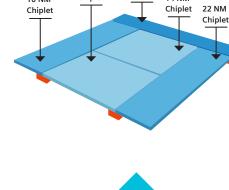

### The Problem: MOORE, is now LESS. Why 3D IC, heterogeneous integration and why the need for homogenous disaggregation? Monolithic (SoC) 2.5D Intergration

defined, is no longer physically possible.

Monolithic scaling,

as it was traditionally

### 14 NM 10 NM Chiplet

We need to meet

the silicon demands

of advanced applications like AI and high-perfor-

chips, as such, we experience increasing yield loss due to their size, and some designs are reaching the reticle size limits.

towards ever-larger

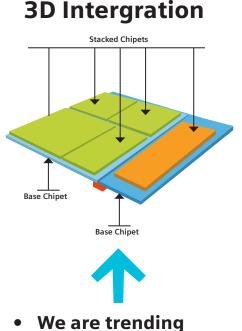

# With today's heterogeneous integration

ecosystem, it is now possible to disaggregate large die into multiple chiplets! What's driving chiplets?

### chiplet" sub-functions Multi-die

implementation

to avoid reticle

limitations (vs.

single die)

into hard IP or "

SOC disaggregation

Verification

Use of High

Bandwidth

High-speed,

chip-to-chip

interfaces

### 3D memory directly stacked on logic

high-bandwidth

Memory (HBM)

**Architecture**

### micro-architecture scenarios Leveraging 2.5

and 3D assembly

Supports multiple

• Chiplet design-in enablement will drive adoption

Mechanical

Integration

platforms

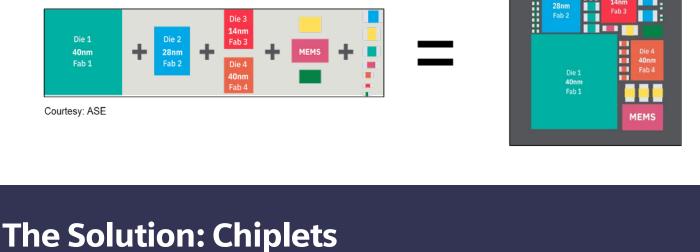

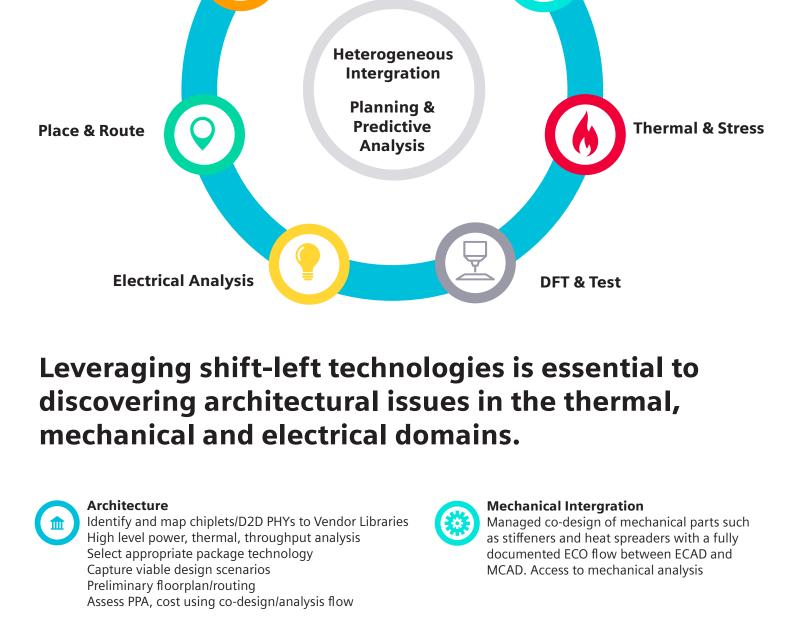

What does the comprehensive chiplet Integration workflow look like?

# interposer, and package substrates

Substrate DRC using PDK

Function verification using LEC Assembly LVS using ADK

Verification

**Place & Route**

Automated interface compliance analysis

What's next

Physical IP reuse and concurrent team-based design **Electrical Analysis** Parasitic extraction, system level power and timing analysis of die, interposer, and package Static/dynamic IR drop and electro-migration analysis

### with accurate package and boundary conditions. Co-simulation and optimization of thermal-mechanical stress effects

technology resources.

Thermal analysis from transistorto

system-level - chiplet, interposer, package,

system. Detailed die-level thermal analysis

**Thermal & Stress**

**DFT & Test** Hierarchical DFT, SSN (Streaming Scan Network), enhanced TAPs (test access ports) and IEEE 1687 IJTAG. Scalable, flexibility, and

ease-to-use, help designers optimize test

Discover how Siemens comprehensive chiplet workflows ensure 3D IC packaging success process that minimizes disruption, risk, and cost!

Learn more

Key benefits for Siemens 3D IC design flow tools scalable, flexibility, and ease-to-use, help designers optimize test technology resources

### 3D IC digital transformation

Enable digital transformation for 3D chip design with co-design, co-simulation and automated system analysis and checking. Replace manual interfaces and data exchanges with automated methods and defined workflows.

Comprehensive 3D IC packaging coverage for performance validation and design verification from predictive to final sign off. Automated reviews identify overt issues earlier in the chip design process and eliminate iterations.

resource utilization Support team-based design for

concurrent development and enable IP reuse and managed blocks. Leverage one chiplet layout tool for organic and silicon substrates for better advanced packaging design.