Are You Struggling to Reach Timing Closure with Your Low Power Design – You May Have CDC Problems!

First, if you were brought here by a desperate Google search for “timing closure tricks STA RTL” as your tape out deadline looms, I can empathize — working to achieve timing closure on a deadline is truly a high pressure, thankless job. Even worse from this standpoint, the addition of vital low power design techniques could unintentionally be the reason why your cycle of analyses and fixes are still not converging — let me explain …

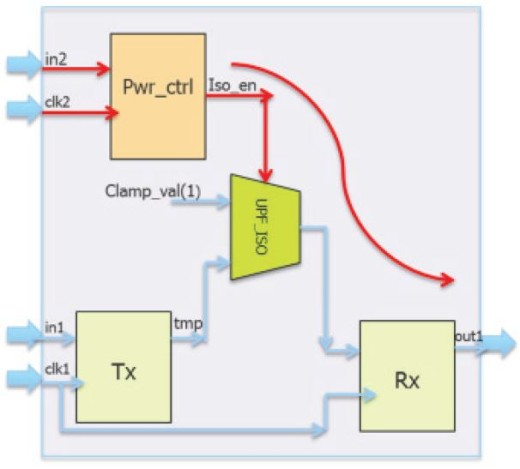

A staple of low power design is to break up a circuit into multiple power domains so dynamic power consumption can be managed, and ultimately reduced. As such, on-command these domains can be electrically isolated from each other so they can be safely shutoff, or run at a lower voltage, or even run at a reduced clock frequency. However, this partitioning – as described by a UPF file and rendered over your design’s RTL – can wreak havoc with your clock and reset signaling networks. Specifically, when clock and reset signals cross power domains they are not synchronous anymore because of the level shifters or isolation cells that have been inserted at the domain interfaces. As such, this can unintentionally give rise to chip killing clock domain crossing (CDC) bugs that would not have otherwise existed.

Additionally, the low power control signals are often aligned to an independent clock that’s part of the low power controller IP – a clock that’s independent of the other clocks in the design. Again, this is a recipe for CDC disaster whether you have a small IoT-related design or a SoC with 100’s of IPs.

Finally, CDC errors often look like static timing problems (if you are not already doing a CDC analysis) – assuming you are lucky enough to see hints of these issues with gate-level simulations before a silicon prototype is minted.

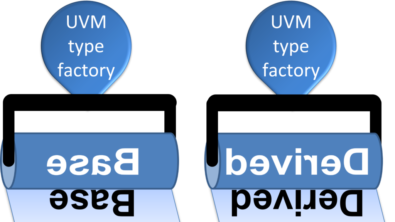

Now for some good news: there are “power aware CDC” methodologies and solutions that can get you out of this mess, such as the “successive refinement” features in the IEEE 1801 low power standard. In a nutshell, these capabilities and the related methodology allows designers to begin the design and verification of power distribution networks at the beginning of the design cycle; and then continue to refine the power networks throughout the project as the circuit implementation comes to life. Alternatively, as in the “tapeout deadline is looming” case, if you are late in the design and implementation cycle it suggests how to execute a “power-aware” CDC analysis. Specifically, designers can run CDC verification for the power distribution networks at the RTL level, and thus avoid dealing with CDC errors at the gate-level, where they are a real pain to analyze. You can find a full article on this topic by CDC and low power methodology expert Kurt Takara at https://goo.gl/dX8Teb

I trust this information will help you get to the real source of your errors, and help you reach your verification goals faster!

Until next time, may all your clock domains be synchronized, and your reset signaling be properly buffered,

Joe Hupcey III

on behalf of the Questa Formal and CDC team

P.S. Kurt’s paper was originally presented at DVCon 2015, March 2015, in San Jose. If you want to get a feel for it, here is a 4 minute video of Kurt walking through the highlights: https://youtu.be/VCyhma3DK4g

Comments