Article Roundup: Joining IIoT Strengths, Design Reuse Vs. Abstraction, Hierarchical CDC Verification, Nondestructive Memory BIST & Texas Instruments History of Innovation

- Joining forces to strengthen IIoT

- Design Reuse Vs. Abstraction

- Raising The Bar On Flat CDC Verification With Hierarchical Data Models

- Nondestructive memory BIST for runtime automotive test

- TI: Semiconductor Industry History of Innovation

Joining forces to strengthen IIoT

Electronics Weekly

The acquisition of Mentor Graphics by Siemens PLM software made immediate sense in the areas of system design and autonomous vehicles. But, as the companies integrate, additional synergies are being discovered in IC design, emulation, and the IoT according to Tony Hemmelgarn, Siemens PLM Software President and CEO, and Wally Rhines, Mentor President and CEO. For the IoT, the natural touchpoint between Siemens and Mentor is at the digital twin, where the companies’ combined capabilities enable customers to model the hardware, electrical, and software components of a product.

The acquisition of Mentor Graphics by Siemens PLM software made immediate sense in the areas of system design and autonomous vehicles. But, as the companies integrate, additional synergies are being discovered in IC design, emulation, and the IoT according to Tony Hemmelgarn, Siemens PLM Software President and CEO, and Wally Rhines, Mentor President and CEO. For the IoT, the natural touchpoint between Siemens and Mentor is at the digital twin, where the companies’ combined capabilities enable customers to model the hardware, electrical, and software components of a product.

Design Reuse Vs. Abstraction

SemiEngineering

For years, the push has been on to find a hardware description language that is a level of abstraction above RTL. The development of this new abstraction level has been delayed because chipmakers are using design reuse to meet the challenges of growing systems design complexity. However, Wally Rhines, CEO of Mentor, maintains that developing designs at higher abstractions is still a viable option. High-level synthesis enables designers to work at the level of C/C++ and perform full system verification before transitioning to RTL.

Raising The Bar On Flat CDC Verification With Hierarchical Data Models

SemiEngineering

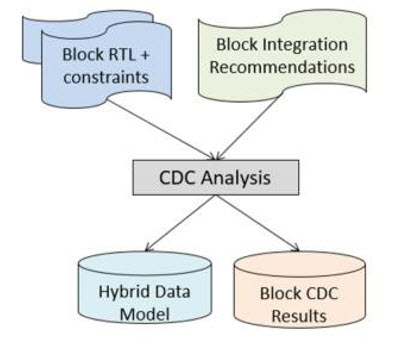

The rising size, speed, and complexity of chip designs are making traditional flat clock domain crossing (CDC) verification obsolete, especially due to the increasing number of asynchronous clocks. Additionally, the proliferation of third-party IP and design reuse shifts the focus from verification of the internals of an IP block to validating that it integrates properly in the system. This article presents a hierarchical CDC verification methodology, which promotes an IP-based flow, to speed up CDC closure.

The rising size, speed, and complexity of chip designs are making traditional flat clock domain crossing (CDC) verification obsolete, especially due to the increasing number of asynchronous clocks. Additionally, the proliferation of third-party IP and design reuse shifts the focus from verification of the internals of an IP block to validating that it integrates properly in the system. This article presents a hierarchical CDC verification methodology, which promotes an IP-based flow, to speed up CDC closure.

Nondestructive memory BIST for runtime automotive test

Evaluation Engineering

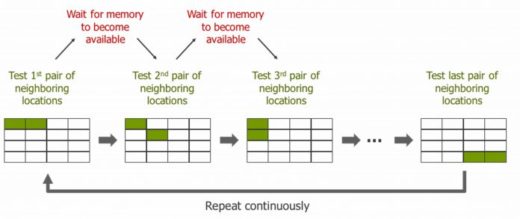

ISO 26262’s functional safety requirements demand that automotive electronics are tested continuously: at ignition, during operation, and when the vehicle is shut down. When it comes to testing memory, system performance can be affected as the system software must disable the target memory, save its contents, then re-enable and restore the memory. Nondestructive memory BIST uses a series of “bursts” to target and test different locations in a memory, allowing testing without affecting the system software performance.

ISO 26262’s functional safety requirements demand that automotive electronics are tested continuously: at ignition, during operation, and when the vehicle is shut down. When it comes to testing memory, system performance can be affected as the system software must disable the target memory, save its contents, then re-enable and restore the memory. Nondestructive memory BIST uses a series of “bursts” to target and test different locations in a memory, allowing testing without affecting the system software performance.

TI: Semiconductor Industry History of Innovation

SemiWiki

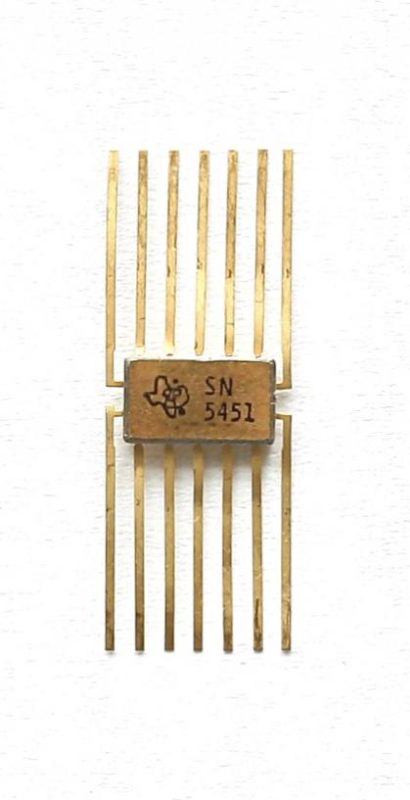

Like Wally Rhines, Texas Instruments has a long history of innovation in the semiconductor industry. Although the company was formed around seismic analysis technology in 1939, the start of World War II saw it transition to making electronic equipment for the U.S. military. After the war, TI purchased a license to produce germanium transistors from Bell Labs and ultimately produced silicon transistors years ahead of the competition. Finally, as a new employee at TI, Jack Kilby took part in creating the first integrated circuit, an effort that would earn him a Nobel Prize.

Like Wally Rhines, Texas Instruments has a long history of innovation in the semiconductor industry. Although the company was formed around seismic analysis technology in 1939, the start of World War II saw it transition to making electronic equipment for the U.S. military. After the war, TI purchased a license to produce germanium transistors from Bell Labs and ultimately produced silicon transistors years ahead of the competition. Finally, as a new employee at TI, Jack Kilby took part in creating the first integrated circuit, an effort that would earn him a Nobel Prize.