Take the Risk out of Signoff with Calibre YieldEnhancer Chip Polishing

By Bill Graupp – Mentor, A Siemens Business

Designing integrated circuits (ICs) today is a complex and high-risk endeavor…

Design teams are large (and often scattered around the world), tool flows are complex, and time-to-market pressures omnipresent; it’s no surprise that product releases are often delayed because design teams can’t get to signoff on schedule. Typically, the final days of signoff are the worst—the deadline is looming, and every iteration between finding and fixing ups the stress level that much more.

As engineers, we’re all about efficiency and lower risk. When considering how to get to signoff faster, there are many ways to do that. You could hire more designers, but that makes coordination harder. You could increase design margins, but that reduces your product’s value. You can make sure to plan plenty of time for final verification and signoff, yet delays earlier in the flow can still impinge on that allotted block of time.

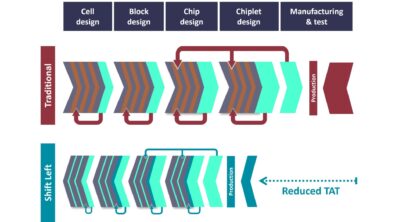

The counterintuitive solution? Add yet another step to the process flow—more verification performed at many levels throughout the design flow to catch and fix problems earlier. The phenomenon of putting in more thought and effort to get “less” isn’t unique to IC design. Mark Twain captured the idea when he said, “I didn’t have time to write a short letter, so I wrote a long one instead.”

But this new step isn’t about adding more work for the verification team—it’s about deploying smarter tools and methods designed to root out issues affecting signoff before they delay your schedule. Many of these issues are not strictly DRC violations, but still cause susceptibility to manufacturing defects. I’m thinking of layout issues such as nano-jogs, space ends, dog bone ends, mushrooms, and offset vias. None of these issues is necessarily a design rule error, but they are likely to affect manufacturability and lower yield.

The Calibre YieldEnhancer tool suite is a solution that’s easy to adopt and customize into any flow, and reduces the risks associated with reaching signoff. It lets designers combine a focused set of commands into macros that can be peppered throughout a customized flow for engineering change order (ECO) filling, passive device insertion, custom fill to increase densities, jog removal, via enhancements, and programmable edge modification (PEM) commands to eliminate fragmented edges. Calibre YieldEnhancer functionality includes unique methods and algorithms that can categorize layout issues by type, and automatically modify the layout to not only significantly reduce final verification runtime, but also improve mask generation while also increasing design robustness and yield.

Many of the failures of today’s post-route sign-off flows can be solved with Calibre YieldEnhancer by creating the conditions for an effective and timely solution to late-stage DRC errors and enabling engineers to insert and modify any shapes needed to achieve the final signoff. A well-designed automated sign-off flow can improve your product’s manufacturability, allow you to get to market faster, and enable you to create market differentiation.

Want more information about how Calibre YieldEnhancer works? Download our new whitepaper The Final Days…Getting to Sign-Off Faster with Calibre. This paper describes our automated chip polishing flow, and how you can create your custom flow to help you get to market faster with better products.